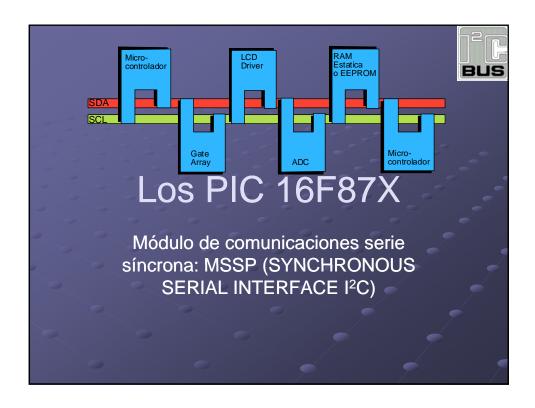

# Módulo de comunicaciones serie síncrona: MSSP

- Puerto Serie Síncrono: Interface de Comunicación Serie Síncrona Pensado para comunicación con otros Microcontroladores o Periféricos:

- EEPROM serie (almacenamiento de datos no volátiles)

- Registros de Desplazamiento (expansión de entradas y/o salidas)

- Drivers de Displays (reducción de conexiones)

- Conversores A/D (digitalización externa de señales)

- ...

- Modos de Operación posibles del módulo SSP:

- SPI (Serial Peripheral Interface): Interface de Periféricos Serie: SPI: Es una Marca Registrada de Motorola Corporation

- I2C (Inter-Integrated Circuit): Entre Circuitos Integrados

I2C: Es una Marca Registrada de Philips

### Generalidades del BUS I<sup>2</sup>C

- Es un interface síncrono a 2 hilos pensado para la comunicación entre C.I. y desarrollado por Philips Corporation. Es un bus estándar para muchos equipos de consumo y telecomunicaciones

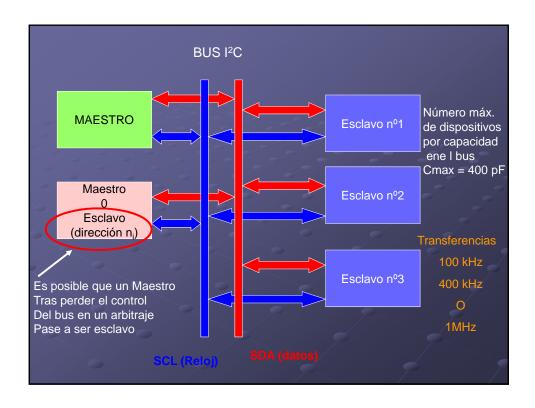

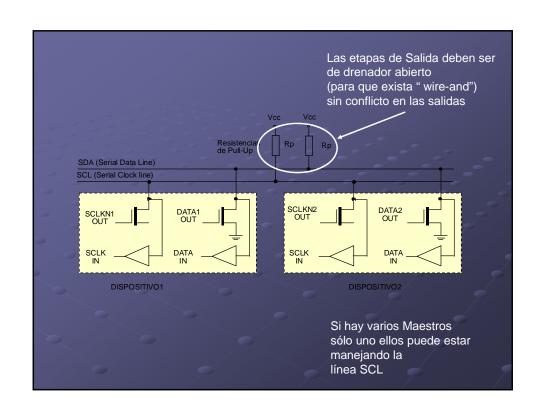

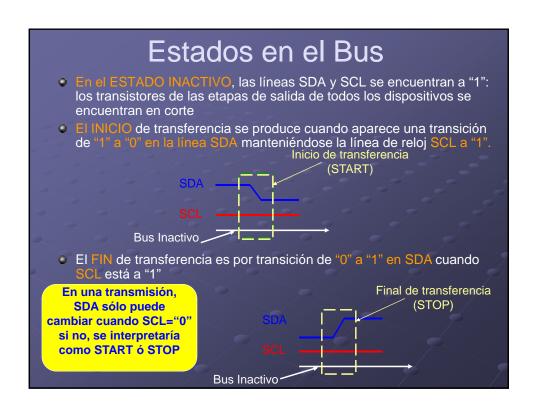

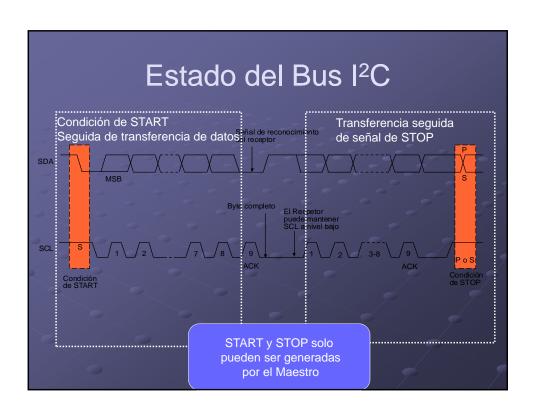

- Las dos líneas de comunicación corresponden a reloj (SCL) y datos (SDA).

- Las transferencias son por tanto semidúplex.

- En el bus debe existir al menos un dispositivo Maestro que genera la señal de reloj y uno o varios Esclavos que reciben tal señal SCL.

- El dispositivo Maestro es el único que tiene capacidad de iniciar la transferencia, decidir con quién se realiza, el sentido de la misma (envío o recepción del Maestro) y cuándo se finaliza

### Generalidades del BUS I<sup>2</sup>C

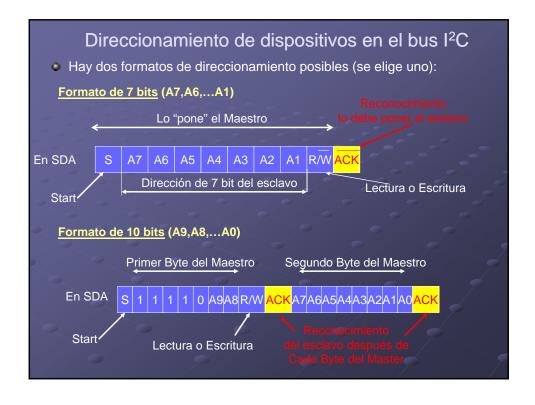

- Cada dispositivo esclavo conectado al bus tiene asignada una dirección única codificada en 7 (ó en 10 bits de manera opcional).

- Se admite la presencia de varios Maestros en el bus (sistema multi-Maestro) con un arbitraje que asegura que en cada instante sólo hay uno dominante

# Comunicación con dispositivos

- Cuando un Maestro decide iniciar una transferencia, envía primero la con el que quiere "hablar"

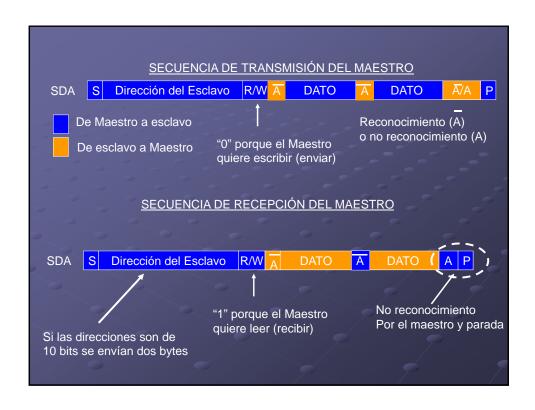

- Todos los dispositivos "escuchan" para determinar si la dirección colocada en el bus es la suya. Acompañando a la dirección aparece un bit R/W que indica al esclavo destinatario si el Maestro quiere "leer" (recibir si R/W=1) del Esclavo o si el Maestro quiere "escribir" (enviar si R/W=0) en el Esclavo.

- El Maestro y el Esclavo direccionado deben encontrarse siempre en

- Maestro emite / Esclavo recibe Maestro recibe / Esclavo emite

- En cualquiera de los casos, el Maestro será el que genere la señal de reloj

- Si hay más de un Maestro en el bus, se debe producir un arbitraje cuando SCL=1: el Maestro que envía un "1" y detecta un "0" en la línea SDA "pierde" en el arbitraje y desactiva su salida de datos (aunque podría seguir generando flancos en la línea SCL hasta que finalizara el envío del byte donde "perdió" el control del bus)

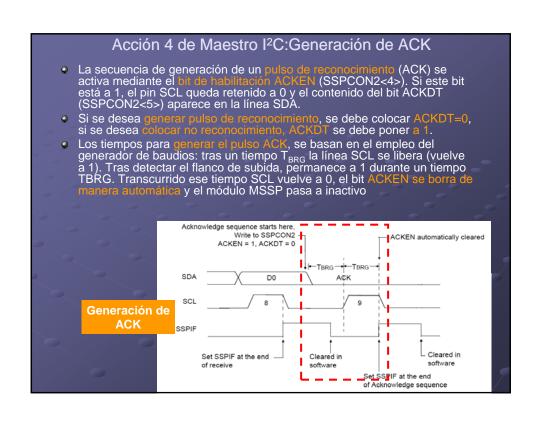

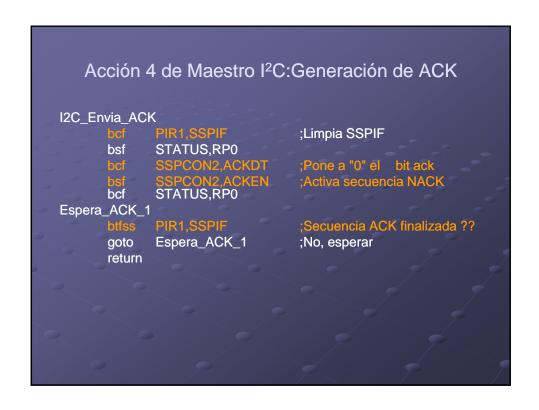

### Reconocimiento de transferencia ACK

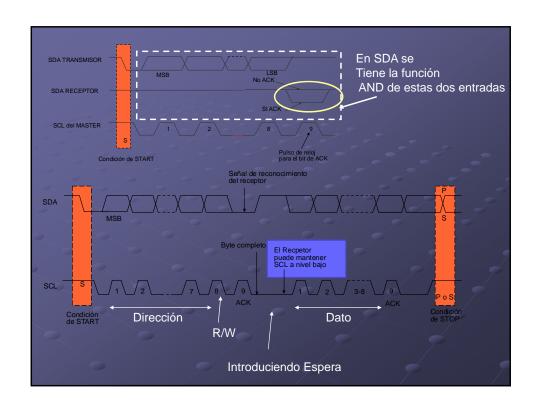

- Los datos se transmiten en paquetes de 8 bits (bytes), no hay límite en cuanto a número de bytes, pero después de cada byte se debe intercalar un bit de reconocimiento (ACK) por parte del dispositivo receptor

- Si es el Esclavo el receptor y no genera el bit de reconocimiento después de cada byte, el Maestro debe abortar la transferencia generando un bit de fin (STOP).

- Dado que las etapas de salida son de drenador abierto, los niveles lógicos "0" son dominantes en las líneas, por tanto el Esclavo debe dejar su salida SDA a "1" para que el Maestro pueda generar el STOP (paso de "0" a "1" con SCL="1").

- Si el dispositivo Maestro es el receptor, genera un ACK tras cada byte recibido, permitiendo al Esclavo que continúe enviando bytes. Si el Maestro decide finalizar la transferencia, genera un bit de STOP en lugar de colocar un bit de reconocimiento

- Si el Esclavo necesita retardar el envío del siguiente byte (porque no lo tiene todavía disponible, p.e.), puede situar la línea SCL en estado bajo y forzar al Maestro a situarse en un estado de "Espera" puesto que no se podrían generar flancos en SCL

### Interface I<sup>2</sup>C de los PIC16F87X

- MSSP Master Synchronous Serial Port, que para el bus I2C implementa:

- Modo Esclavo: Completo por Hw

- Modo Maestro: Completo por Hw

### Módulo MSSP I2C

- Implementa todas las funciones del Maestro y del Esclavo en un bus 12C por hardware

- Permite detectar las condiciones START y STOP en el bus por

- Permite emplear direcciones de 7 ó de 10 bits como Esclavo

- Se puede seleccionar uno de los siguientes modos de operación:

- Esclavo I2C con dirección de 7 bits

- Esclavo I2C con dirección de 10 bits

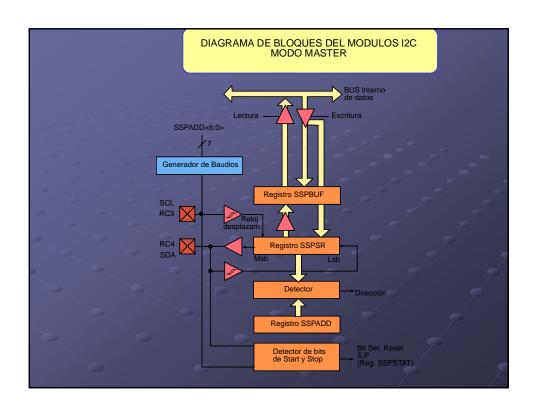

- Maestro I2C con reloj SCL de frecuencia = Fosc/(4\*(SSPADD+1))

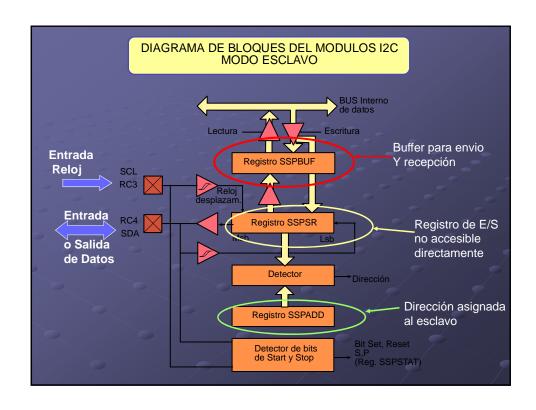

- El módulo MSSP dispone de 6 registros asociados:

- SSPCON Registro de Control

- SSPCON2 Registro de Control 2

SSPSTAT Registro de Estado

SSPADD Registro de Dirección

SSPBUF Buffer de Transmisión/Recepción

SSPSR Registro de Desplazamiento Serie (no accesible)

### Módulo MSSP I2C: Modo Maestro

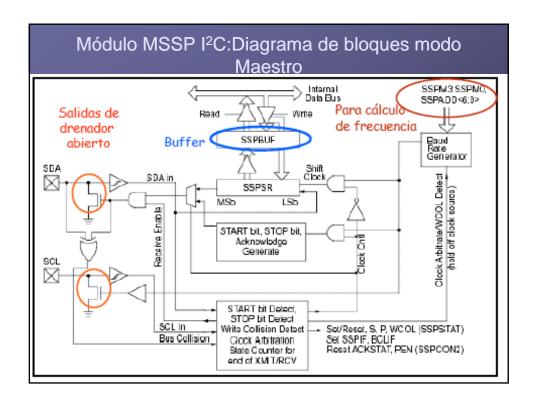

- En modo Maestro, las líneas SDA y SCL son manejadas por el hardware del módulo MSSP, no es necesario definir su dirección en TRISC

- Se dispone de circuitos lógicos para detección de START (S) y STOP (P) y su aparición queda reflejada en los bits S y P de SSPSTAT. Estos bits son de sólo lectura y quedan a cero tras un reset o cuando el módulo MSSP está desactivado.

- El flag SSPIF que permite interrupciones es sensible a los siguientes eventos:

- Condición de START

- Condición de STOP

- Transferencia de un byte

- Transmisión de ACK

- START repetido

### Módulo MSSP I2C: Modo Maestro

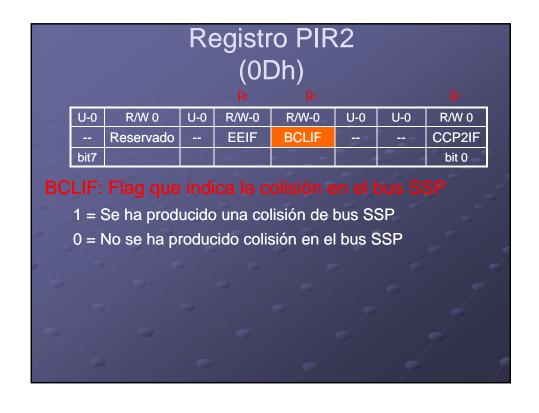

En buses multi-Maestro, el control del mismo sólo puede intentarse cuando el bit P está a 1 ó cuando el bus está inactivo (S y P a "0"). En este caso, la línea SDA será monitorizada para el arbitraje y comprobar si el nivel presente coincide con el nivel esperado y propuesto por el propio Maestro, esta verificación la realiza el hardware y el resultado queda reflejado en el bit de flag de colisiones BCLIF (PIR2<3>) si hay discrepancia y podría generar interrupción (su máscara es BCLIE = PIE2<3>).

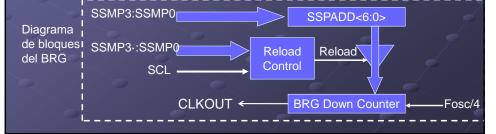

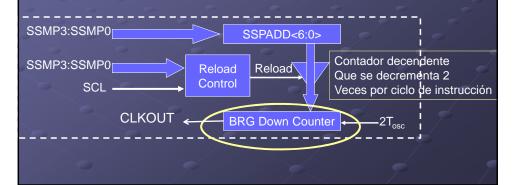

El generador de relación de baudios (BRG) empleado en el modo SPI es el utilizado para generar la frecuencia del reloj SCL. La frecuencia viene dada por la expresión:

$\frac{F_{OSC}}{4*(SSPADD+1)} = \frac{F_{OSC}}{4*(SSPADD+1)}$ En I2C las Frecuencias estándar Son 100 KHz, 400KHz y 1MHz

Se emplean los 7 bits menos significativos del registro SSPADD. En modo Maestro BRG se actualiza automáticamente con el cambio en SSPADD, pero en un bus multi-Maestro, se carga cuando SCL pasa de 0 a estado alto

### 12C Maestro: Generador de relación de Baudios (BRG)

El contador BRG se decrementa dos veces por ciclo de instrucción, y marca un tiempo T<sub>BGR</sub> para establecer secuencias de STOP, START, etc

# I<sup>2</sup>C MAESTRO: Operación

- El Maestro generará los flancos en SCL y las condiciones de START y

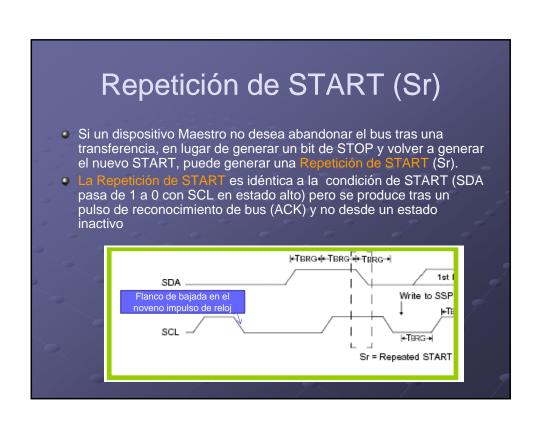

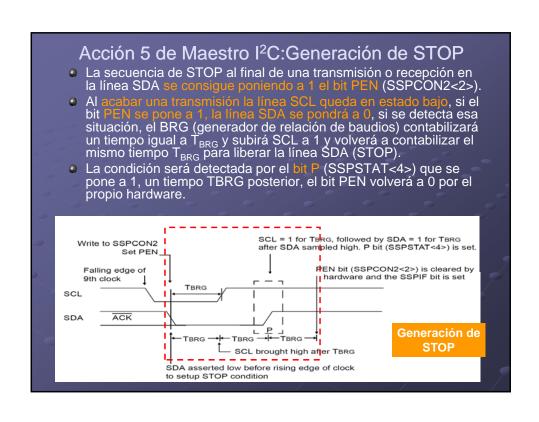

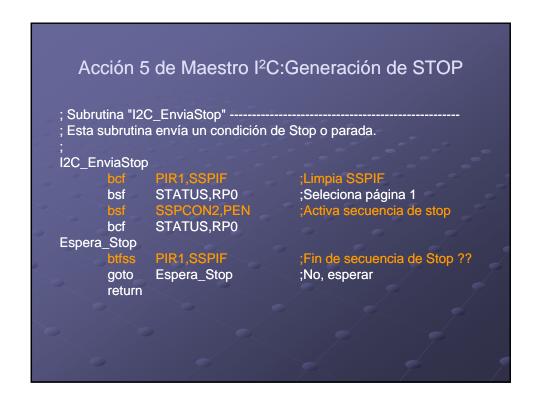

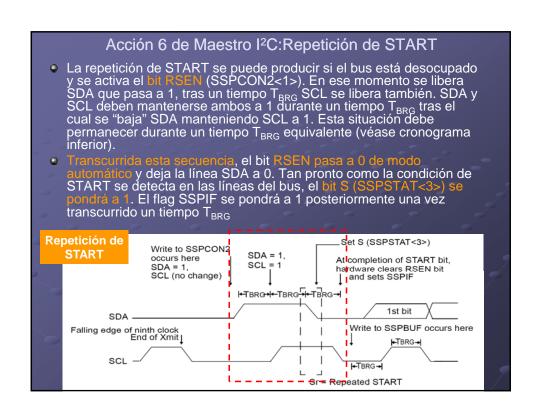

- Una transferencia finaliza con una condición de STOP (P) o con una repetición de START (Sr), en este caso se trata también del inicio de la siguiente transferencia serie con lo que el bus I2C no quedaría libre.

- El modo Maestro f CON y habilitando el módulo con el bit SSPEN. Son posibles 6

- START en las líneas SDA y SCL (bit SEN) Establecer una

- eto en SSPBUF para iniciar una transmisión de dato o dirección

- Configurar la entrada I2C para rec

- Generar un p

- Generar una condición de STOP en SDA y SCL (bit PEN)

Establecer una repetición de START en las mismas líneas (bit RSEN)

- Una acción generada por el Maestro debe esperar a que finalice la anterior (p.e. no se puede escribir el dato en SSPBUF hasta que se haya completado la condición START)

### I<sup>2</sup>C MAESTRO: Operación

- Debe quedar claro que las acciones que va ejecutando el Maestro son totalmente independientes unas de otras.

Como ejemplo: no es posible realizar en un solo paso la generación del bit de START y el envío de la dirección del Esclavo (éstas serían dos acciones

- Para realizar una transferencia completa por parte de un Maestro, emitiendo o recibiendo, será preciso encadenar las diferentes acciones individuales de la manera adecuada, interpretando los resultados obtenidos y los estados presentes en el bus de manera previa a la ejecución de la

- Será necesario que el Maestro compruebe que la acción que él está "intentando" realizar, efectivamente se produce como verificación a su "dominio" sobre el bus

- Si el microcontrolador no dispusiera de módulo MSSP para realizar las acciones por hardware, debería ejecutar cada una de ellas mediante código interno (firmware). También es posible que aún disponiendo de módulo MSSP, se prescinda de la implementación hardware y se realice también en el firmware.

# I<sup>2</sup>C MAESTRO: Operación

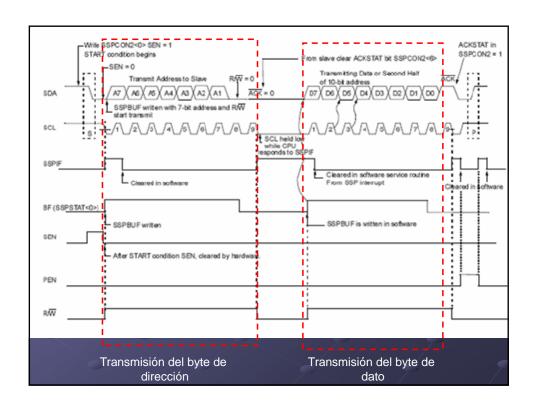

- Ejemplo de Secuencia típica de transmisión de un byte por parte del Maestro:

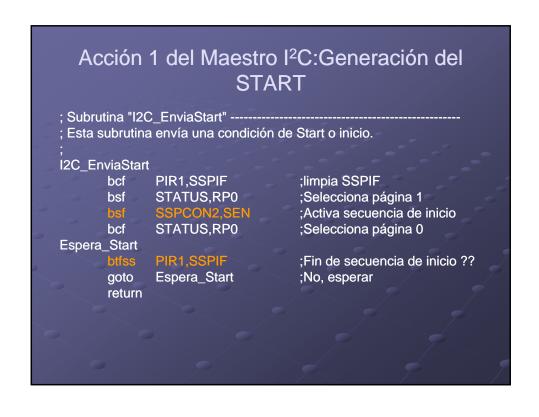

- Se genera START poniendo a 1 el bit de habilitación de START (SEN) del registro SSPCON2

- Se esperará el tiempo necesario para detectar START, cuando se haya dado la condición, SSPIF=1 (se debe poner a 0 por software)

Se carga SSPBUF con la dirección a enviar por el bus y el bit R/W=0 (dir. 7

- Los bits de la dirección van saliendo por la línea SDA hasta completar 8 bits

- Se "lee" el bit simiento (ACK) recibido del esclavo y se introduce ese bit en SSPCON2<6>

- Al final del 9º flanco en SCL, se pone SSPIF=1 (hay que resetearlo)

- g) Se cargan en SSPBUF los 8 bits del dato a enviar

- Los bits del dato van saliendo por SDA hasta completar la transmisión

- Se "lee" el bit de reconocimiento (ACK) y se graba su valor en SSPCON<6>

- Al final del 9º flanco en SCL se pone el flag PIF a 1 (a 0 por programa)

- Se genera una condición de STOP (PEN) de SSPCON2 condición de STOP poniendo a 1 el bit de habilitación de

- Una vez detectada la condición de STOP, se pone a 1 el flag S

### Acción 1 del Maestro l<sup>2</sup>C:Generación del Start Para generar condición de START, el usuario debe poner a "1" el bit SEN (SSPCON2<6>). Si los pines SCL y SDA están a 1, el generador de relación de baudios (BRG) se carga con el contenido de SSPADD<6:0> empezando a decrementarse. Si al llegar al final de la cuenta (T<sub>BRG</sub>) se muestrean SCL y SDA y ambos permanecen a uno, el pin SDA se pone en estado bajo (es por tanto condición de START). Si se detecta la condición generada, el bit S (SSPSTAT<3>) se pone a 1, se cargará a continuación de nuevo BRG y cuando haya transcurrido T<sub>BRG</sub>, el bit SEN se pondrá a 0 por hardware. Si se intenta escribir en SSPBUF durante secuencia de START, entonces bit WCOL=1 y no cambia SSPBUF Si SCL y SDA no estuviera Set S bit (SSPSTAT<3>) a 1, se considera colisión o Write to SEN bit occurs here el BUS (BCLIF=1) se para SDA = 1. At completion of START bit. SCL = 1 la generación de START y Hårdware clears SEN bit and sets SSPIF bit Se pasa a estado inactivo Write to SSPBUF occurs her 12C 1st Bit 2nd Bit SDA \*TBRG\* SCL

### Maestro I<sup>2</sup>C:Colisiones

- Resulta importante distinguir entre los flag WCOL y BCLIF ya que son indicadores de conceptos distintos de colisiones.

- WCOL :es un indicador de "colisión" por acceso al registro SSPBUF debido al intento de escritura en un estado no válido del bus I2C si el dispositivo es Maestro o con intento de escritura en SSPBUF cuando todavía se está enviando un dato anterior

- BCLIF es un indicador de "colisión" en el bus I<sup>2</sup>C (otro tipo por tanto), se produce cuando estando la línea SCL libre, y el estado esperado en SDA es el "1" pero el muestreado resulta ser el "0".

La colisión puede darse durante un START, un STOP o una repetición de START.

BCLIF puede tener asociada una interrupción.

### Acción 2 del Maestro I<sup>2</sup>C: Transmisión de un byte

- El envio de un byte, sea dirección o dato se inicia con la escritura del mismo en el registro SSPBUF. Esto hará que el flag BF se ponga a 1 y que el BRG se ponga en marcha. Cada bit saldrá por SDA en los flancos de bajada de la línea SCL.

- Tras la salida del 8º bit por SDA, el flag BF se pone a 0 y el Maestro "libera" la línea SDA para que el Esclavo direccionado responda con el bit de reconocimiento (ACK).

- El estado ACK se carga en el bit ACKSTAT (=SSPCON2<6>) en el flanco de bajada del 9º pulso en SCL. Tras completar el dato, se da SSPIF=1 y la generación de reloj se suspende hasta que se escriba un nuevo dato en SSPBUF, la línea SCL queda en estado bajo y SDA no cambia

#### Flags en Transmisión

- El flag BF (SSPSTAT<0>) es de solo lectura y se pone a 1 cuando se escribe un byte en SSPBUF, vuelve a 0 cuando hayan sido enviados los 8 bits

- El bit WCOL (SSPCON<7>) es de lectura/escritura y se pone a 1 cuando se intenta escribir en SSPBUF en el transcurso de un envío. Debe ponerse a 0 por software

- El bit ACKSTAT (SSPCON2<6>) es de lectura/escritura, se pone a 0 cuando el esclavo ha enviado un bit de reconocimiento (ACK) y a 1 si no lo ha enviado

### Acción 2 del Maestro I<sup>2</sup>C: Transmisión de un byte ; Subrutina "I2C\_EnviaByte" -; El microcontrolador maestro transmite un byte por el bus I2C, comenzando ; por el bit MSB. El byte a transmitir debe estar cargado previamente en el ;registro de trabajo W. ; De la subrutina ejecutada anteriormente I2C\_EnviaStart o esta misma ;I2C\_EnviaByte, la línea SCL se debe encontrar a nivel bajo al menos durante ;5 µs. 12C\_EnviaByte PIR1,SSPIF ;Limpia SSPIF bcf ;Byte a transmitir pasa al buffer de salida Espera\_Envia\_Byte ;Recibido el bit /ACK ?? goto Espera\_Envia\_Byte ;No, esperar return

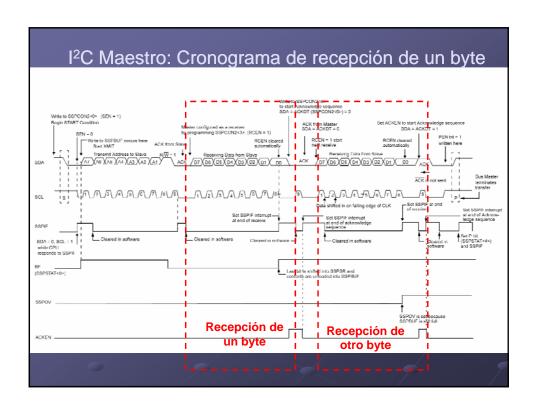

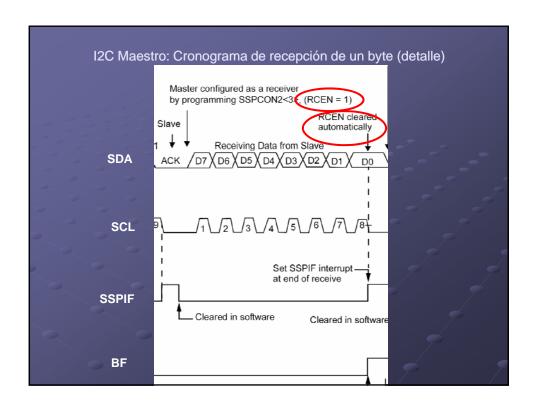

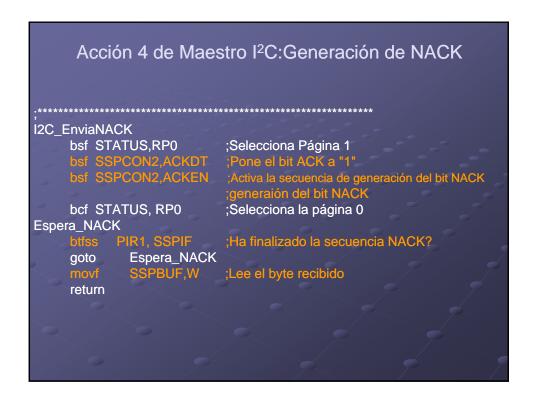

### Acción 3 del Maestro I<sup>2</sup>C: Recepción de un byte

- La recepción de un byte se inicia con la puesta a "1" del bit de habilitación de la recepción RCEN (SSPCON2<3>). Tras esa acción aparecerán los flancos en la línea SCL e irán entrando los bits por la línea SDA.

- Cuando se hayan completado 8 flancos en SCL, el bit RCEN se pondrá a 0 de manera automática, el contenido de SSPSR pasará a SSPBUF y flags BF y SSPIF se pondrán a 1.El reloj dejará de generar flancos, se detendrá y dejará la línea SCL a "0".

- El MSSP quedará ahora inactivo y a la espera de otra acción. Cuando se lea SSPBUF, el flag BF se pondrá a 0 por hardware. El Maestro podría enviar ahora el bit de reconocimiento al final de la recepción poniendo el bit ACKEN=1 (SSPCON2<4>), pero eso ya formaría parte de otra acción

- El flag BF (SSPSTAT<0>) en recepción se pone a 1 cuando se carga SSPBUF desde el registro SSPSR, se pondrá a 0 cuando se haya leído SSPBUF.

- El bit WCOL (SSPCON<7>) se pone a 1 cuando se intenta escribir en SSPBUF cuando una recepción está en curso (SSPBUF no cambia)

- El bit SSPOV (SSPCON<6>) en recepción se pone a 1 cuando se ha completado un dato en SSPSR y el flag BF está todavía a 1 por una recepción previa

```

Acción 3 del Maestro I<sup>2</sup>C: Recepción de un byte

; Subrutina "I2C_LeeByte" -

; Lee un byte procedente del dispositivo I2C selecionado y lo devuelve en W

;Seguidamente se genera y transmite el bit /ACK

I2C_LeeByte

bcf

PIR1,SSPIF

;Restaura el flag del módulo MSSP

bsf

STATUS, RP0

;Selecciona página 1

;Activa el modo recep

;Selecciona página 0

STATUS, RP0

Espera_Lectura

;Recibidos los 8 bits ??

Espera_Lectura

goto

;No, esperar

PIR1,SSPIF

;Restaura el flag del módulo MSSP

bcf

goto

I2C_EnviaNACK

;No, Iniciar I2C_EnviaNACK

STATUS,RP0

bsf

;Selecciona página 1

KDT ;Pone bit ACK a "0"

KEN ;Activa la secuencia de generación del bit ACK

STATUS,RP0

;Selecciona página 0

bcf

Espera_ACK

;Secuencia ACK finalizada ??;No, esperar

Espera_ACK

goto

SSPBUF,W

;Lee el byte recibido

movf

return

```

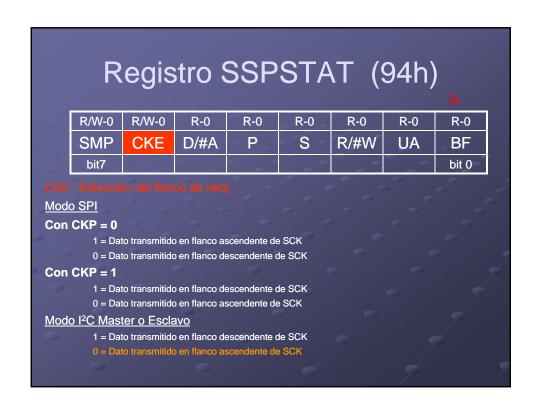

#### Registro SSPSTAT (94h) R/W-0 R/W-0 R-0 R-0 R-0 R-0 R-0 R-0 **SMP** CKE D/#A P S R/#W UA BF bit7 bit 0 **Modo Master** 1 = Muestra datos de entrada al final del tiempo de salida 0 = Muestra datos de entrada a la mitad del tiempo de salida **Modo Esclavo SPI** SMP debe borrarse cuando el SPI se emplea en modo esclavo Modo I<sup>2</sup>C Master o Esclavo 1 = Deshabilita control de variaciones para velocidad estándar (100KHz y 1MHz) 0 = Habilita control (400 KHz)

# Registro SSPSTAT (94h)

**1**30

| R/W-0 | R/W-0 | R-0  | R-0 | R-0 | R-0  | R-0 | R-0   |

|-------|-------|------|-----|-----|------|-----|-------|

| SMP   | CKE   | D/#A | Р   | S   | R/#W | UA  | BF    |

| bit7  |       |      |     |     |      |     | bit 0 |

D/A: Bit de Datos/Direcciones (solo en modo I2C)

1 = Indica el último byte recibido o transmitido es un dato

0 = Indica que el último byte recibido o transmitido es una dirección.

P: Bit de Stop (solo en modo I2C)

1 = Indica que se ha detectado un bit de Stop (este bit es "0" en RESET)

0 = Bit de Stop no detectado

S: Bit de Start (solo en modo I2C)

1 = Indica que se ha detectado un bit de Start

0 = Bit de Stsart no detectado

# Registro SSPSTAT (94h)

1

| R/W-0 | R/W-0 | R-0  | R-0 | R-0 | R-0  | R-0 | R-0   |

|-------|-------|------|-----|-----|------|-----|-------|

| SMP   | CKE   | D/#A | Р   | S   | R/#W | UA  | BF    |

| bit7  |       |      |     |     |      |     | bit 0 |

D/A: Bit de Datos/Direcciones (solo en modo I<sup>2</sup>C)

1 = Indica el último byte recibido o transmitido es un dato

0 = Indica que el último byte recibido o transmitido es una dirección.

P: Bit de STOP (solo en modo I<sup>2</sup>C)

1 = Indica que se ha detectado un bit de Stop (este bit es "0" en RESET)

0 = Bit de Stop no detectado

S: Bit de START (solo en modo l<sup>2</sup>C)

1 = Indica que se ha detectado un bit de Start

0 = Bit de Stsart no detectado

#### Registro SSPSTAT (94h) R/W-0 R/W-0 R-0 R-0 R-0 R-0 R-0 R-0 **SMP** CKE D/#A P S R/#W UA BF bit7 bit 0 I<sup>2</sup>C Modo Esclavo 1 = Escritura 0 = Lectura I<sup>2</sup>C Modo Master 1 = Transmisión en progreso 0 = No hay transmisión en progreso 1 = Indica que es necesario actualizar la dirección en el registro SSPADD 0 = no es necesario actualizar la dirección

### Registro SSPSTAT (94h) R/W-0 R/W-0 R-0 R-0 R-0 R-0 R-0 R-0 **SMP** CKE D/#A P S R/#W UA BF bit7 bit 0 Receptor (Modo SPI e I2C) 1 = Recepción completa SSPBUF está lleno 0 = Recepción no completa el SSPBUF no está lleno **Transmisor (Modo I2C)** 1 = Transmisión en progreso, SSPBUF está lleno (no incluye ACK y bit de 0 = Transmisión completa SSPBUF está vacío (no incluye ACK y bit de Stop)

# Registro SSPCON (14h)

A)

| R/W-0 | R/W-0 | R-0   | R-0 | R-0   | R-0   | R-0   | R-0   |

|-------|-------|-------|-----|-------|-------|-------|-------|

| WCOL  | SSPOV | SSPEN | CKP | SSPM3 | SSPM2 | SSPM1 | SSPM0 |

| bit7  |       |       |     |       |       | · ,   | bit 0 |

### WCOL: Bit de detección de colisión

- 1 = El registro SSPBUF se ha escrito cuando hay una transmisión en proceso (se debe borrar por software)

- 0 = No hay colisión

# Registro SSPCON (14h)

ъ

| R/W-0 | R/W-0 | R-0   | R-0 | R-0   | R-0   | R-0   | R-0   |

|-------|-------|-------|-----|-------|-------|-------|-------|

| WCOL  | SSPOV | SSPEN | CKP | SSPM3 | SSPM2 | SSPM1 | SSPM0 |

| bit7  |       |       |     |       | ٠,    |       | bit 0 |

#### SSPOV: bit de detección de desbordamiento en recepción

#### En modo SPI

1 = Se recibe un nuevo byte cuando el registro SSPBUF aún mantiene los datos anteriores. En caso de desbordamiento, los datos del SSPSR serán falsos, solo puede ocurrir en modo esclavo. Se deberá leer SSPBUF, aún si solo se envían datos, para anular el rebose.

En modo Master el bit no se pone a "1" ya que en cada transmisión o recepción es inicializado por la escritura del registrso SSPBU.

0 = No hay desbordamiento

#### En modo I2C

- 1 = Se recibe un nuevo byte cuando el registro SSPBUF aún mantiene los datos anteriores . En modo transmisión no tiene importancia, en cualquier caso debe borrarse por software

- 0 = No hay desbordamiento

# Registro SSPCON (14h)

H

| R/W-0 | R/W-0 | R-0   | R-0 | R-0   | R-0   | R-0   | R-0   |

|-------|-------|-------|-----|-------|-------|-------|-------|

| WCOL  | SSPOV | SSPEN | CKP | SSPM3 | SSPM2 | SSPM1 | SSPM0 |

| bit7  |       |       |     |       | •     |       | bit 0 |

#### SSPEN: Bit de habilitación del módulo SSP (synchronous Serial Port)

#### En modo SP

- 1 = Habilita puerto serie y configura SCK, SDO y SDI como patillas del puerto serie.

- 0 = Deshabilita el puerto serie y configura estas patillas como puerto de Entrada/Salida

#### En modo I2C

- 1 = Habilita puerto serie y configura SDA y SDL como patillas del puerto serie.

- 0 = Deshabilita el puerto serie y configura estas patillas como puerto de Entrada/Salida

En ambos casos, se deberán configurar como entradas o salidas adecuadamente.

# Registro SSPCON (14h)

70

| R/W-0 | R/W-0 | R-0   | R-0 | R-0   | R-0   | R-0   | R-0   |

|-------|-------|-------|-----|-------|-------|-------|-------|

| WCOL  | SSPOV | SSPEN | CKP | SSPM3 | SSPM2 | SSPM1 | SSPM0 |

| bit7  |       |       |     |       | ٠,    |       | bit 0 |

#### CKP · Bit de selección de polaridad del reloi

#### **EN Modo SPI**

- 1 = Reloj a nivel alto. Transmisión en flanco de bajada, en recepción de subida.

- 0 = Reloj en nivel bajo. Transmisión en flancos de subida por flancos de bajada.

- EN Modo I2C Esclavo (en este modo no se usa como master)

Control de desbloqueo de SCR

- 1 = Habilita reloj

- 0 = Mantiene el reloj a nivel bajo

| K/ VV-U                                 | R/W-0 R/W-0 R-0 R-0 R-0 R-0 R-0                             |                                                                                         |                                                       |          |       |       |       |  |  |  |  |

|-----------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------|----------|-------|-------|-------|--|--|--|--|

| WCOL                                    | SSPOV                                                       | SSPEN                                                                                   | CKP                                                   | SSPM3    | SSPM2 | SSPM1 | SSPM0 |  |  |  |  |

| bit7                                    | bit7 bit 0                                                  |                                                                                         |                                                       |          |       |       |       |  |  |  |  |

| 0110: I<br>0111: I<br>1000: I<br>1011:N | Modo Esclavo<br>Modo Esclavo<br>Modo Master<br>Iodo Esclavo | del SPI, reloj :  12C, direcció 12C, direcció 12C, Reloj = F 12C con sopo 12C, direcció | ón de 7 bits<br>ón de 10 bits<br>fosc/(4x(SSP<br>orte | ADD+1)). |       |       |       |  |  |  |  |

###

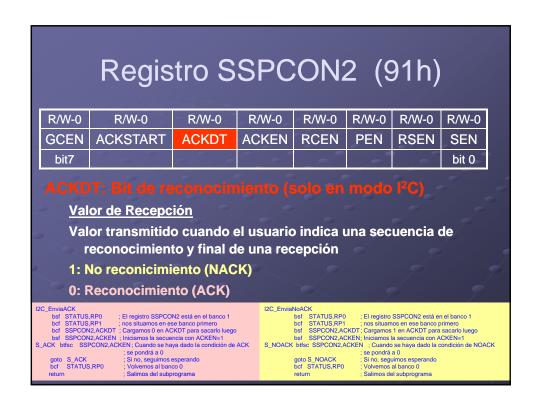

### Registro SSPCON2 (91h) R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 **GCEN ACKSTART ACKDT ACKEN RCEN** PEN **RSEN** SEN bit7 bit 0 Valor de Transmisión 1: Reconocimiento del esclavo no recibido 0: Reconocimiento del esclavo recibido Valor de Recepción 1: No reconocimiento 0: Reconocimiento

# Registro SSPCON2 (91h)

| R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|----------|-------|-------|-------|-------|-------|-------|

| GCEN  | ACKSTART | ACKDT | ACKEN | RCEN  | PEN   | RSEN  | SEN   |

| bit7  |          |       |       |       |       |       | bit 0 |

ACKEN: Bit de habilitación de secuencia de reconocimiento y final de una recepción (solo en modo l²C)

#### Modo de Recepción

- 1: Indica una secuencia de reconocimiento en las patillas SDA y SCL y transmite bit ACKDT. Automáticamente borrado por Hw.

- 0: Secuencia de reconocimiento en reposo.

# Registro SSPCON2 (91h)

| R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|----------|-------|-------|-------|-------|-------|-------|

| GCEN  | ACKSTART | ACKDT | ACKEN | RCEN  | PEN   | RSEN  | SEN   |

| bit7  |          |       |       |       |       |       | bit 0 |

#### RCEN: Bit de habilitación de recepción (solo en modo I2C)

- 1: Habilita recepción en modo I2C, se pone a cero cuando se finaliza.

- 0: Recepción en reposo

#### Registros y bits asociados al Modo I<sup>2</sup>C Address Bit 6 Bit 7 Bit 4 Bit 2 Bit 1 POR, BOR 0Bh, 8Bh, INTCON GIE PEIE TOIE INTE RBIE TOIF 0000 000x 0000 000u 10Bh,18Bh PSPIF(1) ADIF SSPIF 0Ch PIR1 RCIF TXIF CCP1IF TMR2IF TMR1IF 0000 0000 0000 0000 PSPIE<sup>(1)</sup> 8Ch PIE1 ADIE RCIE TXIE SSPIE CCP1IE TMR2IE TMR1IE 0000 0000 0000 0000 0Dh PIR2 (2) FFIF BCLIE CCP2IF -r-0 0--0 8Dh PIE2 EEIE BCLIE (2) CCP2IE -r-0 0--0 -r-0 0--0 13h SSPBUE Synchronous Serial Port Receive Buffer/Transmit Registe 14h SSPCON WCOL SSPOV SSPEN CKP SSPM3 SSPM2 SSPM1 SSPM0 91h SSPCON2 GCEN ACKSTAT ACKDT ACKEN RCEN PEN RSEN 0000 0000 0000 0000 SSPADD I<sup>2</sup>C Slave Address/Master Baud Rate Register 0000 0000 0000 0000 D/Ā CKE Р x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the SSP in I<sup>2</sup>C mode. Note 1: These bits are reserved on PIC16F873/876 devices; always maintain these bits clear 2: These bits are reserved on these devices; always maintain these bits clear.