# 6 EL MODULO TMR1 CON PUERTA DE CONTROL

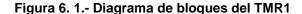

El módulo TMR1 es un temporizador/contador de 16 bits con las siguientes características:

- Temporizador/Contador de 16 bits (TMR1L:TMR1H)

- Programación de la fuente del reloj externo o interno.

- 3 bits de preescaler

- Opción de oscilador LP

- Puede trabajar en modo síncrono o asíncrono

- Puerta de Timer1 (Habilitación del contador) a través d pines de comparación o T1G

- Interrupción por desbordamiento

- Despertar del modo Sleep por desbordamiento (solamente con un reloj externo asíncrono)

- Base de tiempos de para la función de Captura/Comparación

- Disparo eventos especiales (con ECCP)

- La salida del comparador está sincronizada con el reloj de Timer1.

6.1. Funcionamiento de Timer1

El módulo Timer1 es un contadrod incremental de 16 bits al que se accede a través del par de registros TMR1H:TMR1L. Si se escribe directamente en TMR1H o TMR1L se actualiza el contador.

Cuando se utiliza una fuente de reloj interno, el módulo trabaja como temporizador, cuando se utiliza una fuente de reloj externa, el módulo puede utilizarse como temporizador o contador.

### 6.2. Selección de Fuente de reloj

El bit RMR1CS del registro T1CON se utiliza para seleccionar la fuente del reloj. Cuando TMR1CS=0, la fuente del reloj es FOSC/4. Cuando TMRCS=1, la fuente del reloj es externa.

| Fuente de reloj | TMR1CS |

|-----------------|--------|

| FOSC/4          | 0      |

| Pin T1CKI       | 1      |

### **6.2.1 FUENTE DEL RELOJ INTERIOR**

Cuando la fuente de reloj que se selecciona es la interna, los registros TMR1H:TMR1L se incrementa a la FOSC multiplicado por el preescaler del Timer1.

### **6.2.2 FUENTE DEL RELOJ EXTERNA**

Cuando se selecciona le fuente de reloj externa, el Timer1 puede trabajar como temporizador o contador.

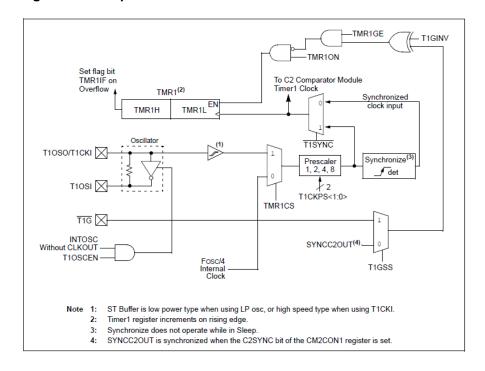

En el modo contador, el Timer1 se incrementa en el flanco de subida de la señal de reloj externa introducida por T1CLKI. Además, el reloj en modo contador puede sincronizarse con el reloj del sistema o puede ser asíncrono.

Si es necesario un oscilador externo (El microcontroldor utiliza INTOSC sin CLKOUT), el Timer1 puede usar el oscilador LP como fuente de reloj.

En modo contador, se debe detectar un flanco descendente antes del primer flanco de subida que incrementa el contador después de las condicione siguientes (ver Figura 6.2):

- El Timer1 se habilita después de un Reset por POR o BOR

- Una escritura de TMR1H o TMR1L

- Cuando T1CKI está a nivel alto y el Timer1 está deshabilitado o cuando el se habilita TMR1 y T1CKI está a nivel bajo.

### 6.3. Preescaler del Timer1

El Timer1 tiene cuatro opciones de preescaler que permiten dividir la señal de reloj por 1, 2, 4 u 8. Los bits T1CKPS del registro T1CON controlan el preescaler del contador. El contador del preescaler no se puede leer o escribir directamente; sin embargo, el contador del preescaler se limpia cuando se escribe en TMR1H o TMR1L.

### 6.4. Oscilador del Timer1

Un oscilador low-power de 32.768 se puede realizar entre los pines T1OSI (entrada) y T1OSO (salida del amplificador). El oscilador se habilita poniendo a "1" el bit T1OSCEN del registro T1CON. El oscilador continuará funcionando aunque esté en el

microcontrolador en moco Sleep.

EL oscilador del Timer1 es idéntico al oscilador LP.

El usuario debe realizar un retardo por software para asegurar un correcto funcionamiento del oscilador.

Los bits TRISC0 y TRISC1 se fijan cuando el oscilador del Timer1 está habilitado. Los bits RC0 y RC1 se leen como "0" y los bits TRISC0 y TRISC1 se leen como 1.

Nota.- El oscilador requiere un tiempo desde su puesta en marcha para estabilizarse antes de su uso. Así T1OSCEN debe ponerse a "1" y después de un tiempo prudencial habilitar el Timer1.

# 6.5. Funcionamiento del Timer1. Modo contador Asíncrono

En modo contador asíncrono se debe poner a "1" el bit de control T1SYNC del registro T1CON, la entrada de reloj externa no se sincroniza. ΕI temporizador incrementándose de forma asíncrona a las fases internas del reloj. El cronometro sigue incrementándose aunque esté en modo sleep y puede generar una interrupción por desbordamiento que despierta al procesador. necesario embargo, es tener precauciones especiales en el software al leer/escribir en el Timer1 (Ver sección 6.5.1. "Lectura y Escritura del Timer1 en el modo Contador Asíncrono").

Nota: Al cambiar de modo síncrono a modo asíncrono, es posible salta un incremento. Al cambiar de asíncrono al funcionamiento síncrono, es posible producir un incremento espurio.

## 6.2.3 LECTURA Y ESCRIBIÉNDOLE A TIMER1 EN EL MODO DEL CONTADOR ASÍNCRONO

Leer TMR1H o TMR1L mientras el reloj asíncrono externo del temporizador está corriendo asegura una lectura válida (teniendo precaución con el harware). Sin embargo, el usuario debe tener en cuenta que al leer un temporizador de 16 bits de con dos registros de 8 bits, tiene ciertos problemas, ya que el temporizador puede desbordarse entre lecturas.

Para escribir, se recomienda que el usuario Para el Timer1 y escriba los valores deseados. Puede darse un problema al escribir el temporizador mientras este se incrementa. Esto puede producir un valor imprevisible en la pareja de registros TMR1H:TMR1L.

#### 6.6. La Puerta del Timer1

La puerta de disparo del Timer1 es configurable por software para que sea T1G o la salida del Comparador C2. Esto permite al dispositivo cronometrar eventos externos que utilizan T1G o los eventos analógicos que utilizan el Comparador C2 directamente.

Ver el registro CM2CON1 (Registro 8-3) para seleccionar la puerta de disparo de Timer1. Esta característica puede simplificar el software para un Delta-Sigma del conversor A/D y muchas otras aplicaciones. Para más información sobre Delta-Sigma en los convertidores A/D, ver la web de Microchip (www.microchip.com).

Nota: El bit TMR1GE del registro T1CON debe ponerse a "1" para usar la puerta del Timer1.

El nivel que activa el Timer1 puede invertirse con el bit T1GINV del registro T1CON, Ya sea del pin T1G o de la salida del Comparador C2. Esto configura Timer1 para medir el tiempo entre eventos por flanco de subida o flanco de bajada.

### 6.7. Interrupción del Timer1

El par de registros del Timer1 (TMR1H:TMR1L) al incrementar FFFFh se desborda y pasa a 0000h. Cuando el Timer1 se desborda, el flag de interrupción del Timer1 del registro PIR1 se pone a "1". Para habilitar la interrupción en la configuración se

deben realizar estos pasos:

Habilitar el bit de interrupción del Timer1 en el registro PIE1

Poner a "1" el bit PEIE del registro INTCON Poner a "1" el bit GIE del registro INTCON

El programa de atención a la interrupción deberá de poner a "0" el bit TMR1IF

Nota: La pareja de registros TMR1H:TMR1L deben ponerse a cero y el bit de TMR1IF antes de habilitar las interrupciones.

La nota: Los TMR1H:TTMR1L registran deben aclararse par y el pedazo de TMR1IF antes de habilitar las interrupciones.

Funcionamiento del Timer1 en modo Sleep

# 6.8. Funcionamiento de Timer1 Durante el modo Sleep

El Timer1 solo puede salir del modo sleep cuando está configurado como Contador Asíncrono. En este modo, un cristal externo o una fuente externa de reloj incrementa el contador. Para preparar el temporizador para salir del modo sleep:

El bit TMR1ON del registro T1CON debe ponerse a "1"

El bit TMR1IE del registro PIE1 debe ponerse a "1"

El bit PEIE del registro INTCON debe ponerse a "1".

El dispositivo sale del modo sleep al desbordarse y se ejecuta la siguiente instrucción. Si el el bit GIE del registro INTECON se pone a "1", el dispositivo ejecuta la rutina de atención a la interrupción (0004h).

# 6.9. Base de tiempos del ECCP en modo Captura/Comparación

El módulo ECCP utiliza el par de registros TRM1H:TMR1L como base de tiempos cuando trabaja en el modo de Captura o Comparación

En el modo Captura, el par de registros TMR1H:TMR1L se copia en el par de registros CCPRxH:CCPRxL al producirse un evento configurado.

En el modo Comparación, se activa un evento cuando el valor del par de registros CCPRxH:CCPRxL coinciden con el valor del par de registros TMR1H:TMR1L. Este evento puede ser el disparo de un Evento Especial.

Para más información vea la Sección 11.0 "Capture/Compare/PWM"

### 6.10. ECCP Disparo por Evento Especial

Si se configura el ECCP para activarse por un evento especial, el disparo limpiará el par de registros TMR1H:TMR1L. Este evento especial no causa una interrupción del Timer1. El módulo ECCP puede configurarse para generar una interrupción del ECCP.

En este modo de funcionamiento el par de registros CCPRxH:CCPRxL funcionan como registro de periodo para el Timer1.

El Timer1 debe sincronizarse con la FOSC para utilizar el disparo por Evento Especial. El funcionamiento asíncrono del Timer1 puede causar un disparo por Evento Especial extraño.

En el caso de que una escritura en TMR1H o TMR1L coincida con el disparo por Evento Especial del ECCP, la escritura tomará el valor anterior.

Para más información ver la sección 11.0 "Los módulos de Captura/Comparación/PWM (CCP1 y CCP2)."

### 6.11. Sincronización de Comparador

El mismo reloj que incrementa el Timer1,

suele utilizarse para sincronizar la salida del comparador. Esta característica se habilita en el módulo Comparador.

Al utilizar el comparador para disparar la puerta del Timer1, la salida del comparador debe sincronizarse con el Timer1. Esto asegura que el Timer1 no realice incrementos extraños en el comparador

Para más información, ver la Sección 8.0 "el Módulo de Comparator."

Figura 6. 2.- Flanco de Incremento del TIMER1

# 6.12. Registro de Control del Timer1 (T1CON)

El Registro de Control del Timer1 se utiliza para control del Timer1 y seleccionar varias características del módulo TIMER1.

## REGISTRO T1CON: Registro de control del TIMER1 (dirección 10h)

U-0 U-0 RW-0 R/W-0 R/W-0 R/W-0 R/W-0

T1GINV

-- T1CKPS1

T1CKPS0

T1OSCEN

T1SYNC

TMR1CS

TMR1ON

Bit 7

Bit 0

Bit7: **T1GNV**: bit de Inversión del disparo de la puerta del Timer1<sup>(1)</sup>

1 = El disparo del Timer1 es por flanco de subida (Timer1 cuenta cuando la puerta esta a "1")

0 = El disparo del Timer1 es por flanco de baja dala (Timer1 cuenta cuando la puerta está a cero)

bit 6: TMR1GE: bit que habilita la puerta del Timer1<sup>(2)</sup>

### Con TMR1ON = 0:

Se ignora

### <u>Con TMR1ON = 1:</u>

1 = La cuenta del Timer1 se controla por la puerta de disparo del Timer1

0 = Timer1 siempre está contando

bit 5-4: TICKPS1:T1CKPS0: bit de selección del preescaler de la señal de reloj del TIMER1

11 = valor del preescaler 1:8

10 = valor del preescaler 1:4

01 = valor del preescaler 1:2

00 = valor del preescaler 1: 1

bit 3: T10SCEN: bit de habilitación del oscilador LP.

1 = Habilita el oscilador LP como reloj del TMR1

0 = Deshabilita el oscilador LP

bit 2: **TISYNC**: bit de control de sincronización de la señal de entrada.

## $\underline{\text{Con TMR1CS}} = 1$

1= No sincroniza la entrada de reloj externa

0 = Sincroniza la entrada de reloj externa

### Con TMR1CS = 0

En esta condición se ignora. El TIMER1 utiliza el reloj interno cuando TMR1CS=0

bit 1 TMR1CS: bit de selección de la fuente de reloj del TIMER1

1 = Reloj externo por el pin RC0/T1OSO/T1CK1 (flanco ascendente)

0 = Reloj interno (FOSC/4)

bit 0: **TMR10N**: TIMER1 activo. Hace entrar o no en funcionamiento el TIMER1.

1 = Habilita el TIMER1

0 = Deshabilita el TIMER1

#### notas

1: el bit T1GINV invierte la puerta lógica del Timer1, sin tener en cuenta la fuente.

2: El bit e TMR1GE debe ponerse a "1" para usar el pin T1G o C2OUT, y seleccionar el bit T1GSS del registro CM2CON1, como puerta de disparo del TMR1.

TABLE 6-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1

| Name    | Bit 7                                                                       | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-----------------------------------------------------------------------------|--------|---------|---------|---------|--------|--------|-----------|----------------------|---------------------------------|

| CM2CON1 | MC10UT                                                                      | MC2OUT | C1RSEL  | C2RSEL  | _       | _      | T1GSS  | C2SYNC    | 000010               | 000010                          |

| INTCON  | GIE                                                                         | PEIE   | TOIE    | INTE    | RBIE    | TOIF   | INTF   | RBIF      | 0000 000x            | 0000 000x                       |

| PIE1    | _                                                                           | ADIE   | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE | TMR1IE    | -000 0000            | -000 0000                       |

| PIR1    | _                                                                           | ADIF   | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF | TMR1IF    | -000 0000            | -000 0000                       |

| TMR1H   | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register  |        |         |         |         |        |        |           | xxxx xxxx            | uuuu uuuu                       |

| TMR1L   | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |        |         |         |         |        |        | XXXX XXXX | uuuu uuuu            |                                 |

| T1CON   | T1GINV                                                                      | TMR1GE | T1CKPS1 | T1CKPS0 | T10SCEN | T1SYNC | TMR1CS | TMR10N    | 0000 0000            | uuuu uuuu                       |

$\textbf{Legend:} \qquad \textbf{x} = \textbf{unknown}, \ \textbf{u} = \textbf{unchanged}, \ \textbf{-} = \textbf{unimplemented}, \ \textbf{read as '0'}. \ \textbf{Shaded cells are not used by the Timer1 module}.$